以下是关于 Xilinx Zynq UltraScale+ ZU19EG 异构计算平台的详细介绍,基于AMD-Xilinx官方技术资料和行业应用案例整理:

---

1. 核心概览

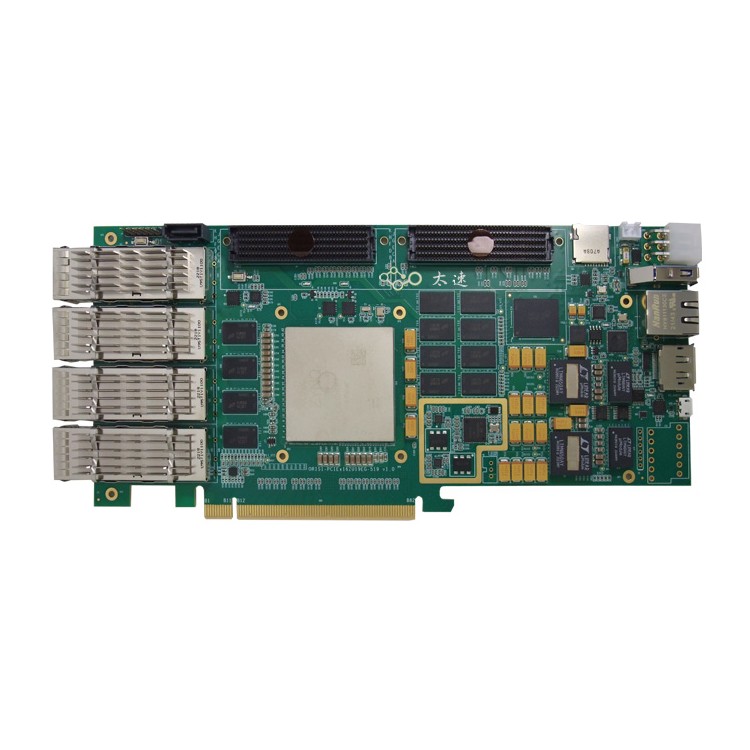

- 产品定位:Zynq UltraScale+ MPSoC系列高性能型号,融合ARM处理器与FPGA逻辑

- 关键特性:

✅ 四核Cortex-A53 + 双核Cortex-R5 + Mali-400 GPU

✅ 1.1M可编程逻辑单元(等效Artix-7规模)

✅ 16Gbps收发器 + PCIe Gen3x8硬化模块

✅ 车规级选项(-40°C~+125°C)

---

2. 硬件规格

| 模块 | 参数 |

|------------------------|-----------------------------------|

| 处理系统(PS) | 四核A53 @1.5GHz + 双核R5 @600MHz |

| 可编程逻辑(PL) | 1,143K LUTs / 2,184 DSP Slices |

| 内存接口 | 64bit DDR4-2400(支持ECC) |

| 高速接口 | 16×16Gbps GTY + 8×6Gbps SATA |

| 视频编解码 | H.264/H.265 4K60硬件加速 |

| 封装功耗 | FFVC1760(功耗范围5W-30W) |

---

3. 架构优势

3.1 异构计算分工

- A53集群:运行Linux/裸机应用(如协议栈)

- R5核:实时控制(电机驱动/安全监控)

- FPGA逻辑:硬件加速(算法卸载)

3.2 高速互联

- AXI一致性端口(ACP):

- 支持PS与PL缓存一致性(加速数据交换)

- 片上NoC:

- 256位总线(32GB/s带宽)

---

4. 典型应用场景

- 自动驾驶:

- 多传感器融合(激光雷达+摄像头预处理)

- 工业4.0:

- 机器视觉(PL运行OpenCV硬件流水线)

- 通信设备:

- 5G小基站基带处理(A53跑协议栈,PL做FFT加速)

---

5. 开发支持

5.1 工具链

- Vitis 2023.2:

- 支持C/C++/Python统一开发(AI加速库集成)

- PetaLinux:

- 预配置Yocto层支持GPU驱动

5.2 评估套件

- ZCU104:

- 板载4K HDMI接口 + 8GB DDR4

- 提供端到端视频流水线参考设计

---

6. 性能对比(vs 竞品)

| 场景 | ZU19EG性能 | Intel Cyclone 10 GX | 优势 |

|------------------|------------------|---------------------|---------------------|

| 视频分析 | 4K60 H.265编码 | 仅支持1080p | 硬件编解码单元 |

| 实时控制 | 双核R5锁步运行 | 无硬核实时处理器 | 功能安全ASIL-D达标 |

| 能效比 | 3.5 TOPS/W | 2.1 TOPS/W | FPGA优化算法卸载 |

---

7. 设计注意事项

1. 电源树设计:

- 需11路电源(推荐TI TPS650864 PMIC)

- PS内核电压0.85V±2%精度要求

2. DDR4布线:

- 长度匹配控制在±50ps(推荐HyperLynx仿真)

3. 热管理:

- 30W工况需2oz铜厚+散热过孔阵列

---

8. 技术文档

- [数据手册DS925](https://www.xilinx.com/zu19eg-ds925)

- [Zynq UltraScale+ TRM UG1085](https://www.xilinx.com/ug1085)

- [Vitis AI用户指南UG1414](https://www.xilinx.com/vitis-ai-ug1414)

---

9. 应用案例

- 特斯拉HW3.0:用于自动驾驶传感器预处理(同系列ZU5EG)

- 华为5G微波:实现基带与射频一体化设计

如需具体的异构任务划分或功耗优化方案,可提供进一步需求!

通过中商114

通过中商114

冀公网安备13010402002588

冀公网安备13010402002588