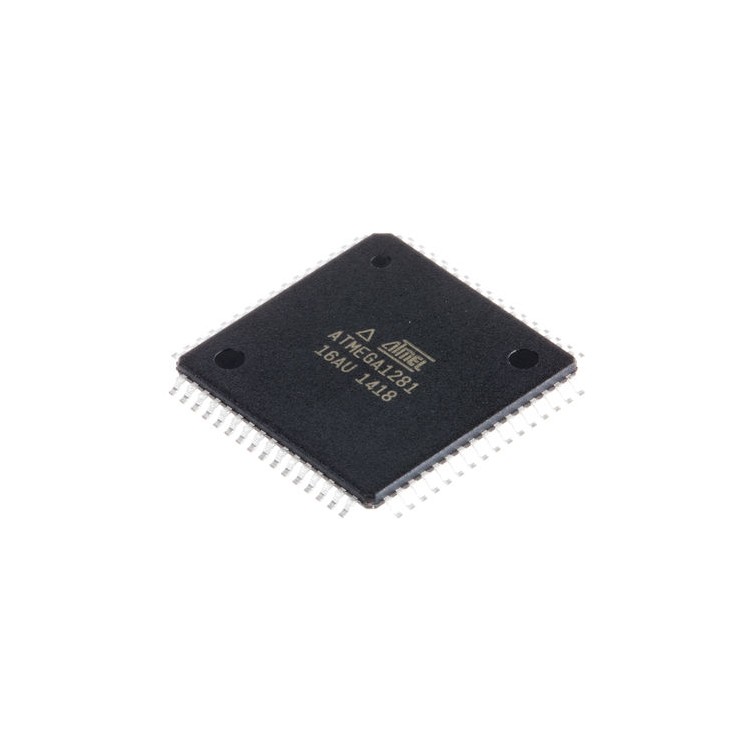

STM32F405RGT6 高性能微控制器深度解析

核心规格

| 参数 | 规格 |

|------|------|

| 内核 | Cortex-M4 @168MHz (带FPU) |

| 存储 | 1MB Flash + 192KB SRAM |

| 加密引擎 | 无 (需软件实现) |

| 通信接口 | 3x SPI/3x I2C/6x USART |

| 高级外设 | USB OTG FS/HS + CAN 2.0B |

| 封装 | LQFP64 (10x10mm) |

架构亮点

1. 双AHB总线架构

```

总线矩阵

├─ AHB1 (高速外设) → GPIO/定时器/DMA1

└─ AHB2 (USB/Camera) → 独立带宽分配

```

2. 实时性能

- 中断响应:仅12个时钟周期

- DMA控制器:2个(各8通道)

- PWM分辨率:168MHz下可达4.76ns

3. 存储特性

- Flash加速:ART加速器实现零等待

- CCM RAM:64KB核心耦合内存(无总线竞争)

开发资源

1. 硬件工具

- NUCLEO-F405RG (ST-link/V2-1调试)

- DISCO-F407G (含音频编解码器)

- 专用电机控制套件

2. 软件生态

| 组件 | 说明 |

|------|------|

| STM32CubeF4 | HAL/LL库+中间件 |

| FreeRTOS | 优化内存占用仅5KB |

| STM32CubeMX | 引脚配置工具 |

性能实测

- CoreMark:562分 @168MHz

- DSP性能:

- 1024点FFT:0.57ms

- FIR滤波:1.8M taps/s

- 功耗表现:

- 运行模式:100mA @全速

- 停机模式:20μA

设计要点

1. 电源配置

```text

+3.3V ─┬─ VDD

├─ VBAT (RTC)

└─ VDDA (ADC基准)

```

- 去耦电容要求:

- 每VDD引脚100nF

- 全局10μF钽电容

2. PCB布局规范

- 层数要求:至少4层

- 高频信号:

- USB DP/DM差分对90Ω阻抗

- 时钟线长度≤50mm

- ADC布线:

- 独立模拟地平面

- 远离数字信号1.5mm以上

典型应用方案

1. 四轴飞行器控制

```c

// PWM输出配置(TIM1)

htim1.Instance->CCR1 = motor1_speed;

htim1.Instance->CCR2 = motor2_speed;

HAL_TIM_PWM_Start(&htim1, TIM_CHANNEL_ALL);

```

2. USB音频设备

```

USB HS → I2S → CS43L22 DAC

↑

SAI接口(音频流)

```

选型对比

| 型号 | 关键差异 | 适用场景 |

|------|----------|----------|

| F405RGT6 | 性价比平衡 | 通用控制 |

| F407VGT6 | 带加密引擎 | 安全应用 |

| F415RGT6 | 无PHY USB | 成本敏感型 |

生命周期:持续量产至2028年

官方资源:[STM32F405产品页面](https://www.st.com/en/microcontrollers-microprocessors/stm32f405-415.html)

通过中商114

通过中商114

冀公网安备13010402002588

冀公网安备13010402002588